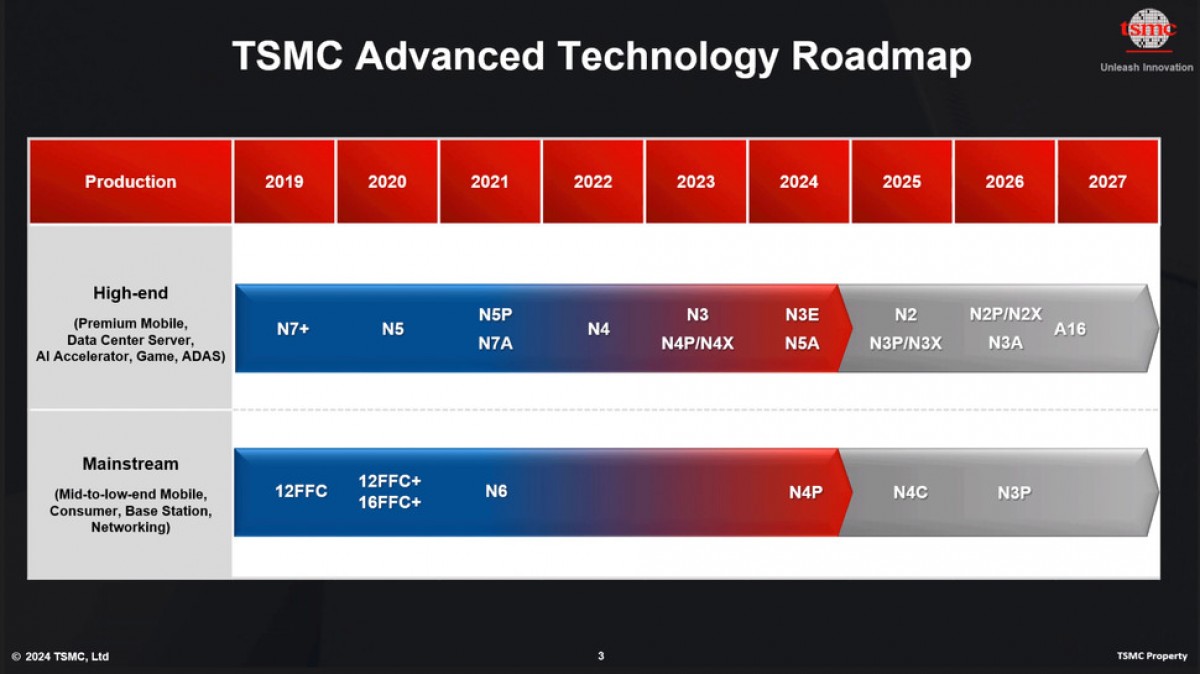

TSMC introduced its ground-breaking 1.6nm manufacturing course of for chips and it additionally consists of bottom energy supply community that improves energy effectivity and transistor density even additional.

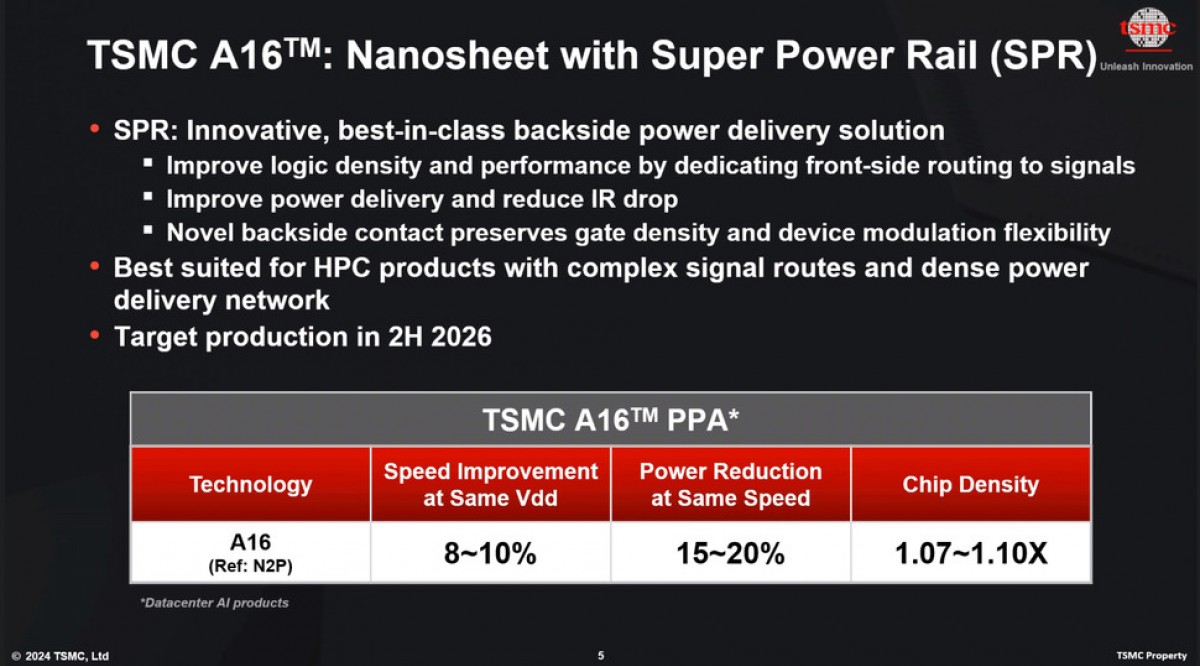

The introduced 1.6nm course of depends on gate-all-around nanosheet transistors, identical to the upcoming N2, N2P and N2X architectures based mostly on the 2nm node. The brand new course of alone permits 10% greater clock speeds on the similar voltage and as much as 20% decrease energy drain on the similar frequency and complexity. Relying on the chip design, the brand new 1.6nm course of also can match as much as 10% extra transistors.

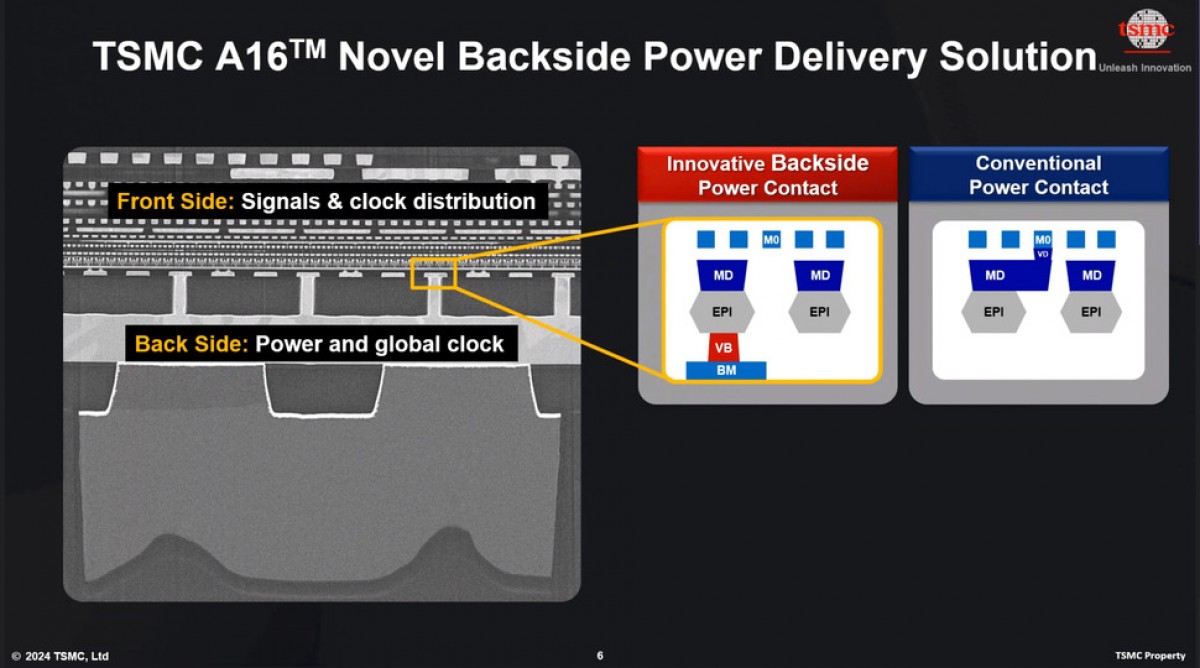

The bottom energy supply community is arguably an much more spectacular facet of those future chips because it permits elevated transistor density and improved energy supply, which in flip impacts efficiency. TSMC says that together with the Tremendous Energy Rail (SPR), which is the kind of plug used to conncect the chip to the ability supply, the bottom energy supply community will show useful largely to AI and HPC processors that require complicated sign wiring and dense energy networks.

The manufacturing timeline is scheduled for the second half of 2026, if all goes to plan, with the primary consumer-ready merchandise transport in 2017.

Leave a Comment